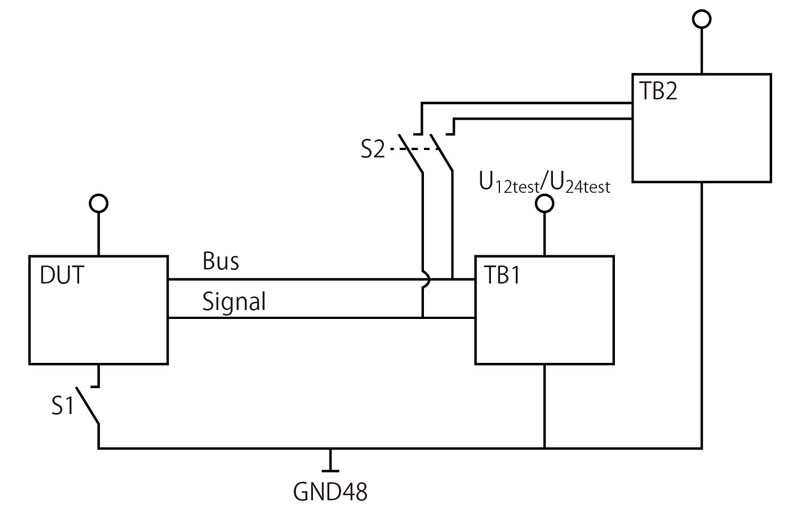

この試験は、BN48から独占的に供給され、BN12/BN24コンポーネントとのインタフェース(例:CAN/LIN/FlexRayバス、その他のアナログまたはデジタル信号線)を持つBN48コンポーネントシステムの損失をシミュレートします。BN48コンポーネントシステムの損失が他のBN12 / BN24の通信に干渉しない(例:過電圧または極性反転による)ことに加えて、損失がいかなる部品にも破壊的な影響を与えないことも保証される必要があります。

| ttest | see tests |

| U48test | U48n |

| Ttest | Tmax – 20 ℃ |

| Number of cycles per test | 1 |

| Number of DUTs | 6 |

S1 closed.

S2 closed.

All components DUT / TB1 / TB2 work without errors.

S2 is openp

There must be errors in TB1 and TB2 :

– TB1 : Bus communication with TB2 is interrupted

– TB2 : Bus communication interrupted with TB1

– TB2 : Signal lines interrupted

No error in DUT – functional state A.

S1 closed.

S2 closed.

All components DUT / TB1 / TB2 work without errors.

S1 is opened.

The test takes 30 minutes after opening S1.

“In TB1 and TB2, no voltages may exceed the defined interface voltages and no currents above the defined interface current may occur. This applies to all bus and signal lines.

Bus communication: The bus communication between TB1 and TB2 works error-free – no error in the error memory.”

Signal line:

Case distinction

A) DUT reads this line, that is, TB1 is the transmitter.

Requirement: No error entry in TB1 and TB2.

B) DUT is the transmitter.

Requirement: Incorrect entry in TB1 and TB2 due to loss of the signal.